Product Summary

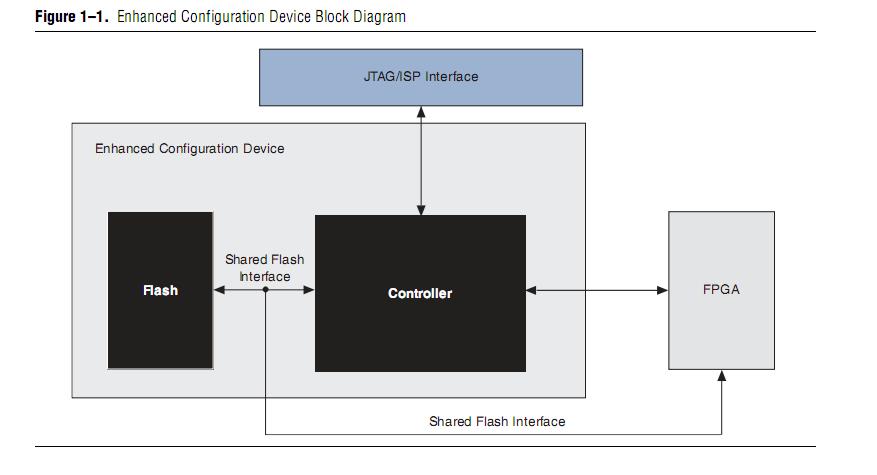

The EP20K200EQC208-2X is a single-device, high-speed, advanced configuration solution for very high-density FPGA. The core of EP20K200EQC208-2X is divided into two major blocks: a configuration controller and a flash memory. The flash memory is used to store configuration data for systems made up of one or more Altera FPGAs.

Parametrics

EP20K200EQC208-2X absolute maximum ratings: (1)Supply voltage With respect to ground:-0.2V to 4.6V; (2)DC input voltage With respect to ground:-0.5V to 3.6V; (3)DC VCC or ground current:100 mA; (4)DC output current, per pin:-25mA to 25mA; (5)Power dissipation:360 mW; (6)Storage temperature No bias: -65℃ to 150℃; (7)Ambient temperature Under bias:-65℃ to 135℃; (8)Junction temperature Under bias:135℃.

Features

EP20K200EQC208-2X features: (1)Contains 4-, 8-, and 16-Mbit flash memories for configuration data storage; (2)On-chip decompression feature almost doubles the effective configuration density; (3)Standard flash die and a controller die combined into single stacked chip package; (4)External flash interface supports parallel programming of flash and external processor access to unused portions of memory ; (5)Flash memory block/sector protection capability via external flash interface; (6)Supported in EPC16 and EPC4 devices; (7)Page mode support for remote and local reconfiguration with up to eight configurations for the entire system; (8)Compatible with Stratix series Remote System Configuration feature; (9)Supports byte-wide configuration mode fast passive parallel(FPP); 8-bit data output per DCLK cycle; (10)Supports true n-bit concurrent configuration (n = 1, 2, 4, and 8) of Altera FPGAs; (11)Pin-selectable 2-ms or 100-ms power-on reset (POR) time ; (12)Configuration clock supports programmable input source and frequency synthesis; (13)Supports ISP via Jam Standard Test and Programming Language(STAPL); (14)Supports JTAG boundary scan; (15)nINIT_CONF pin allows private JTAG instruction to start FPGA configuration; (16)Internal pull-up resistor on nINIT_CONF always enabled; (17)User programmable weak internal pull-up resistors on nCS and OE pins; (18)Internal weak pull-up resistors on external flash interface address and control lines, bus hold on data lines; (19)Standby mode with reduced power consumption.

Diagrams

|

EP2001-9R |

|

EURO-CASSETTE 120W 2X 5.1V |

Data Sheet |

|

|

||||||||||||

|

EP201 |

Other |

|

Data Sheet |

Negotiable |

|

||||||||||||

|

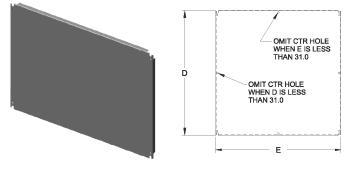

EP2012 |

Hammond Manufacturing |

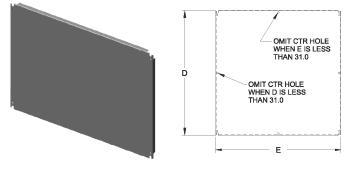

Electrical Enclosure Accessories E PANEL FITS 20X1224 |

Data Sheet |

Negotiable |

|

||||||||||||

|

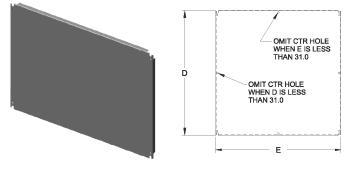

EP2016 |

Hammond Manufacturing |

Electrical Enclosure Accessories E-PANEL FITS 20 X 16 |

Data Sheet |

|

|

||||||||||||

|

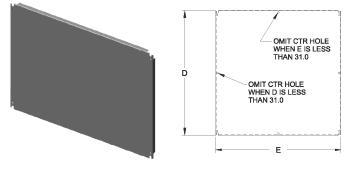

EP2020 |

Hammond Manufacturing |

Electrical Enclosure Accessories E-PANEL FITS 20 X 20 |

Data Sheet |

|

|

||||||||||||

|

EP2024 |

Hammond Manufacturing |

Electrical Enclosure Accessories E-PANEL FITS 20 X 24 |

Data Sheet |

|

|

||||||||||||

(China (Mainland))

(China (Mainland))